- PCIe® Management Interface (PCIe-MI®) over MCTP Binding Specification

- <sup>2</sup> Version: 1.0.0

- 3 Document Identifier: DSP0291

- 4 Date: 2025-06-12

- 5 Version History: https://www.dmtf.org/dsp/DSP0291

- 6 Supersedes: None

- 7 Document Class: Normative

- 8 Document Status: Published

- 9 Document Language: en-US

Copyright Notice

Copyright © 2025 DMTF. All rights reserved.

- DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. Members and non-members may reproduce DMTF specifications and documents for uses consistent with this purpose, provided that correct attribution is given. As DMTF specifications may be revised from time to time, the particular version and release date should always be noted.

- Implementation of certain elements of this standard or proposed standard may be subject to third-party patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations to users of the standard as to the existence of such rights and is not responsible to recognize, disclose, or identify any or all such third-party patent right owners or claimants, nor for any incomplete or inaccurate identification or disclosure of such rights, owners, or claimants. DMTF shall have no liability to any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, disclose, or identify any such third-party patent rights, or for such party's reliance on the standard or incorporation thereof in its products, protocols, or testing procedures. DMTF shall have no liability to any party implementing such standards, whether such implementation is foreseeable or not, nor to any patent owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is withdrawn or modified after publication, and shall be indemnified and held harmless by any party implementing the standard from any and all claims of infringement by a patent owner for such implementations.

- For information about patents held by third-parties which have notified DMTF that, in their opinion, such patents may relate to or impact implementations of DMTF standards, visit https://www.dmtf.org/about/policies/disclosures.

- CXL® and Compute Express Link® are registered trademarks of the Compute Express Link Consortium. IETF® is a registered trademark of IETF Trust. ISO® is a registered trademark of the International Organization for Standardization (ISO). MIPI® and I3C® are registered trademarks owned by MIPI Alliance. The NVM Express® and NVMe® word marks are registered service marks of the NVM Express organization in the United States and other countries. All rights reserved. PCI-SIG®, PCI Express®, PCIe®, and PCIe-MI® are registered trademarks or service marks of PCI-SIG. The SMBus name is a mark of System Management Interface Forum (SMIF), Inc.

- 14 This document's normative language is English. Translation into other languages is permitted.

#### CONTENTS

| 1 Foreword                                              | 4 |

|---------------------------------------------------------|---|

| 1.1 Acknowledgments                                     | 4 |

| 2 Introduction                                          | 5 |

| 2.1 Document conventions                                | 5 |

| 2.1.1 Typographical conventions                         | 5 |

| 2.1.2 ABNF usage conventions                            | 5 |

| 3 Scope                                                 |   |

| 4 Normative references                                  |   |

| 5 Terms and definitions                                 |   |

| 6 Symbols and abbreviated terms                         |   |

| 7 Conventions                                           |   |

| 7.1 Reserved and unassigned values                      |   |

| 7.2 Byte ordering                                       |   |

| 8 Overview                                              |   |

| 8.1 General                                             |   |

| 9 Message type-specific considerations                  |   |

| 9.1 Message type number                                 |   |

| 9.2 PCIe-MI over MCTP specification version information |   |

| 9.3 Timing specifications                               |   |

| 9.4 PCIe-MI over MCTP message format                    |   |

| 9.4.1 PCIe-MI over MCTP message field descriptions      |   |

| 9.4.2 Message assembly                                  |   |

| 9.5 Maximum message body size                           |   |

| 9.6 Multiple MCTP physical transports                   |   |

| 10 ANNEX A (informative) Change Log                     |   |

|                                                         |   |

## <sup>15</sup> 1 Foreword

- The *PCIe Management Interface (PCIe-MI) over MCTP Binding Specification* (DSP0291) was prepared by the Platform Management Communications Infrastructure (PMCI Working Group) of DMTF.

- DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. For information about DMTF, see <a href="https://www.dmtf.org">https://www.dmtf.org</a>.

- PCI-SIG® is a community responsible for developing and maintaining a standardized approach for peripheral component I/O data transfers. For information about PCI-SIG, see <a href="https://pcisig.com">https://pcisig.com</a>.

### 1.1 Acknowledgments

- 20 DMTF acknowledges the following individuals for their contributions to this document:

- 21 Editor:

- · Austin Bolen Dell Technologies

- 22 Contributors:

- · Patrick Caporale Lenovo

- Eliel Louzoun Intel Corporation

- · Hemal Shah Broadcom Inc.

## <sup>23</sup> 2 Introduction

The PCIe® Management Interface (PCIe-MI®) over MCTP Binding Specification defines an MCTP message type used to transport PCIe-MI payloads to or from PCIe-compatible components over MCTP.

#### 2.1 Document conventions

#### 26 2.1.1 Typographical conventions

- 27 This document uses the following typographical conventions:

- · Document titles are marked in italics.

- Important terms that are used for the first time are marked in italics.

- Terms include a link to the term definition in the "Terms and definitions" clause, enabling easy navigation to the term definition.

- · ABNF rules are in monospaced font.

#### 28 2.1.2 ABNF usage conventions

- 29 Format definitions in this document are specified using ABNF (see RFC5234), with the following deviation:

- Literal strings are to be interpreted as case-sensitive Unicode characters, as opposed to the definition in RFC5234 that interprets literal strings as case-insensitive US-ASCII characters.

# 30 3 Scope

- The PCIe Management Interface (PCIe-MI) over MCTP Binding Specification defines a binding in order to transport PCIe-MI messages to or from PCIe elements over MCTP. The specific PCIe-MI message contents will be documented outside of DMTF directly by PCI-SIG.

- Portions of this specification rely on information and definitions from other specifications, which are identified in the Normative references clause. The following references are particularly relevant:

- DMTF DSP0236, Management Component Transport Protocol (MCTP) Base Specification 1.3, defines the MCTP transport protocol over which the PCIe-MI messages are to be transported.

### 4 Normative references

- The following referenced documents are indispensable for the application of this document. For dated or versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies. For references without a date or version, the latest published edition of the referenced document (including any corrigenda or DMTF update versions) applies. Earlier versions may not provide sufficient support for this specification.

- DMTF DSP0218, Platform Level Data Model (PLDM) for Redfish Device Enablement 1.1, https://www.dmtf.org/sites/default/files/standards/documents/DSP0218 1.1.pdf

- DMTF DSP0233, Management Component Transport Protocol (MCTP) I3C Transport Binding Specification 1.0, https://www.dmtf.org/sites/default/files/standards/documents/DSP0233\_1.0.pdf

- 37 DMTF DSP0235, NVMe (NVM Express) Management Messages over MCTP Binding Specification 1.0, https://www.dmtf.org/sites/default/files/standards/documents/DSP0235 1.0.pdf

- 38 DMTF DSP0236, *Management Component Transport Protocol (MCTP) Base Specification 1.3*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0236 1.3.pdf

- DMTF DSP0237, Management Component Transport Protocol (MCTP) SMBus/I2C Transport Binding Specification 1.2, https://www.dmtf.org/sites/default/files/standards/documents/DSP0237 1.2.pdf

- DMTF DSP0238, Management Component Transport Protocol (MCTP) PCle VDM Transport Binding Specification 1.2, https://www.dmtf.org/sites/default/files/standards/documents/DSP0238\_1.2.pdf

- 41 DMTF DSP0239, Management Component Transport Protocol (MCTP) IDs and Codes 1.9, https://www.dmtf.org/sites/default/files/standards/documents/DSP0239 1.9.pdf

- DMTF DSP0240, *Platform Level Data Model (PLDM) Base Specification 1.1*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0240\_1.1.pdf

- DMTF DSP0241, *Platform Level Data Model (PLDM) over MCTP Binding Specification 1.0*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0241 1.0.pdf

- DMTF DSP0248, *Platform Level Data Model (PLDM) for Platform Monitoring and Control Specification 1.2*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0248 1.2.pdf

- DMTF DSP0261, *NC-SI over MCTP Binding Specification 1.2*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0261\_1.2.pdf

- DMTF DSP0267, *Platform Level Data Model (PLDM) for Firmware Update Specification 1.2*, https://www.dmtf.org/sites/default/files/standards/documents/DSP0267 1.2.pdf

- DMTF DSP0281, CXL (Compute Express Link) Type 3 Device Component Command Interface over MCTP Binding Specification 1.0, https://www.dmtf.org/sites/default/files/standards/documents/DSP0281 1.0.pdf

- DMTF DSP0283, MCTP over USB Binding Specification 1.0, https://www.dmtf.org/sites/default/files/standards/documents/DSP0283 1.0.pdf

- DMTF DSP4014, *DMTF Process for Working Bodies*, https://www.dmtf.org/sites/default/files/standards/documents/DSP4014.pdf

- 50 IETF RFC4122, A Universally Unique IDentifier (UUID) URN Namespace, July 2005, https://www.ietf.org/rfc/rfc4122.txt

- 51 IETF RFC5234, ABNF: Augmented BNF for Syntax Specifications, January 2008, https://tools.ietf.org/html/rfc5234

- ISO/IEC Directives, Part 2, *Rules for the structure and drafting of ISO and IEC documents*, https://www.iso.org/sites/directives/current/part2/index.xhtml

- 53 PCI-SIG, PCI Express® Base Specification, https://www.pcisig.com/specifications

# 5 Terms and definitions

- In this document, some terms have a specific meaning beyond the normal English meaning. Those terms are defined in this clause.

- The terms "shall" ("required"), "shall not", "should" ("recommended"), "should not" ("not recommended"), "may", "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described in ISO®/IEC Directives, Part 2, Clause 7. The terms in parentheses are alternatives for the preceding term, for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that ISO/IEC Directives, Part 2, Clause 7 specifies additional alternatives. Occurrences of such additional alternatives shall be interpreted in their normal English meaning.

- The terms "clause", "subclause", "paragraph", and "annex" in this document are to be interpreted as described in ISO/IEC Directives, Part 2, Clause 6.

- The terms "normative" and "informative" in this document are to be interpreted as described in ISO/IEC Directives,

Part 2, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do not contain normative content. Notes and examples are always informative elements.

- Refer to the MCTP Base Specification (DSP0236) for terms and definitions that are used across the MCTP specifications.

- Refer to the PCI Express Base Specification for terms and definitions applicable to PCIe-MI. For the purposes of this document, the following additional terms and definitions apply.

- 61 Endpoint

- 62 An MCTP endpoint unless otherwise specified.

- 63 PCI Express (PCIe)

- An industry-standard low-latency high-bandwidth serial expansion bus for connecting peripheral components to a computer system.

- 65 PCIe Management Interface (PCIe-MI)

- A management interface defined by PCI-SIG to manage PCIe-compatible components in a PCIe system.

# 6 Symbols and abbreviated terms

- Refer to the MCTP Base Specification (DSP0236) for symbols and abbreviated terms that are used across the MCTP specifications. Refer to the PCI Express Base Specification for symbols and abbreviated terms applicable to PCIe-MI. For the purposes of this document, the following additional symbols and abbreviated terms apply.

- 69 **MCTP**

- 70 Management Component Transport Protocol

- 71 **PCle**

- 72 PCI Express

- 73 PCIe-MI

- 74 PCIe Management Interface

# <sup>75</sup> 7 Conventions

### 76 7.1 Reserved and unassigned values

- Unless otherwise specified, any reserved, unspecified, or unassigned values in enumerations or other numeric ranges are reserved for future definition by DMTF.

- Unless otherwise specified, numeric or bit fields that are designated as reserved shall be written as 0 (zero) and ignored when read.

### 79 7.2 Byte ordering

Unless otherwise specified, the byte ordering of multibyte numeric fields or multibyte bit fields in this specification shall be "Big Endian" (i.e., the lowest byte offset holds the most significant byte and higher offsets hold lesser significant bytes).

## 8 Overview

#### 82 **8.1 General**

- PCI Express (PCIe) is an industry-standard low-latency, high-bandwidth serial expansion bus for connecting peripheral components to a computer system. The PCIe Management Interface (PCIe-MI) protocol is used for the configuration, control, and status functions in PCIe-compatible components. The PCIe-MI payloads are defined by the PCI Express Base Specification and the members of PCI-SIG. Refer to https://pcisig.com for more information.

- This specification only defines how PCIe-MI commands are encapsulated in MCTP messages and transferred between MCTP Endpoints over transports that have a corresponding MCTP transport binding specification which is referred to in this document as PCI Management Interface (PCIe-MI) over MCTP. The definitions and semantics of the PCIe-MI payloads themselves are outside the scope of this specification and are defined in the PCI Express Base Specification.

- The MCTP Transport Bindings that are used for PCIe-MI over MCTP are defined in other companion specifications including but not limited to the MCTP SMBus®/I2C Transport Binding Specification (DSP0237), the MCTP I3C® Transport Binding Specification (DSP0233), the MCTP PCIe VDM Transport Binding Specification (DSP0238), and the MCTP over USB Binding Specification (DSP0283).

# 9 Message type-specific considerations

### 9.1 Message type number

The message type number for PCle-MI messages is defined in the MCTP IDs and Codes Specification (DSP0239) and the number assigned is 0x09.

### 9.2 PCIe-MI over MCTP specification version information

- Implementations that follow this specification shall return the following version information in the response to the GET MCTP Version Support command when the Message Type parameter in the request is set to 0x09 (return PCI Management Interface (PCIe-MI) over MCTP Specification version information).

- The Version Number Entry 1 field shall be used to indicate compatibility with Version 1.0 of the PCIe-MI over MCTP message type as:

- 92 1.0 [Major version 1, minor version 0, any update version, no alpha]

- This is reported using the encoding as: 0xF1F0FF00

### 94 9.3 Timing specifications

PCIe-MI over MCTP messages are made up of one or more MCTP packets. Each MCTP packet shall comply with the timing, arbitration, and fairness requirements of the transport binding specifications for the media through which it passes. For examples, refer to the specific MCTP physical layer binding specification (for example the MCTP SMBus/I2C Transport Binding Specification (DSP0237), the MCTP I3C Transport Binding Specification (DSP0233), the MCTP PCIe VDM Transport Binding Specification (DSP0238), and the MCTP over USB Binding Specification (DSP0283), among others) for specific packet and message timing requirements.

### 96 9.4 PCIe-MI over MCTP message format

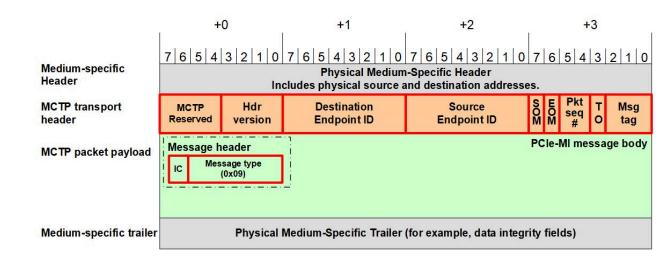

97 Referring to Figure 1, the PCIe-MI over MCTP messages are carried via the MCTP packet payload of one or more MCTP packets.

99

100

101

102

Figure 1 — PCIe-MI over MCTP Message Fields in an MCTP Packet

#### 9.4.1 PCIe-MI over MCTP message field descriptions

PCIe-MI message fields shall comply with the requirements in the MCTP Base Specification (DSP0236) and with the additional requirements indicated in Table 1.

Table 1 — PCle-MI over MCTP Message Field Descriptions

| Field Name                    | Field Size | Description                                                                                                                                                                                                                                                  |

|-------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tag Owner (TO)                | 1 bit      | 1b - PCIe-MI Command messages.  0b - PCIe-MI Completion messages. A PCIe-MI Completion message shall use the destination EID and physical address that were used as the source EID and source physical address of the corresponding PCIe-MI Command message. |

| Message Tag ( <u>Msg</u> tag) | 3 bits     | When PCIe-MI message exchange is used and the Tag Owner (TO) bit is set to 1b in the PCIe-MI Command message, a PCIe-MI Completer shall return the same Message Tag with the Tag Owner bit cleared to 0b in the corresponding PCIe-MI Command message.       |

| Integrity Check (IC)          | 1 bit      | Message Integrity Check bit = 0b. PCIe-MI over MCTP messages do not include an overall Message Integrity check field.                                                                                                                                        |

| Message type                  | 7 bits     | The PCIe-MI over MCTP message type number shall be set to 0x09.  This field identifies the MCTP message as carrying a PCIe-MI over MCTP message.                                                                                                             |

| PCIe-MI message body          | Variable   | Other than the message type field and the IC bit, the PCIe-MI message body is defined by PCIe-MI.                                                                                                                                                            |

For the definition of PCIe-MI Command Message, PCIe-MI Completion Message, and the PCIe-MI message body other than the message type field and the IC bit, refer to the PCI Express Base Specification.

#### 104 9.4.2 Message assembly

PCIe-MI over MCTP messages may be split into one or more MCTP packets thus requiring segmentation and assembly. All multi-packet PCIe-MI over MCTP messages shall comply with the message packetization and assembly rules of the MCTP Base Specification (DSP0236). Specifically, sections in the MCTP Base Specification (DSP0236) related to Message assembly, Dropped packets, Starting message assembly, Terminating message assembly/dropped messages, and Dropped messages shall be complied with. PCIe-MI messages when transported over MCTP shall not require any changes to the MCTP Base Specification (DSP0236).

### 9.5 Maximum message body size

- The PCIe-MI over MCTP message body shall be less than or equal to 4224 (4K+128) bytes. All MCTP endpoints that support PCIe-MI shall support this maximum message body size of 4224 bytes. This corresponds to a transfer of 66 MCTP packets using a baseline transmission unit of 64 bytes for the MCTP packet payload. See the PCI Express Base Specification for a definition of the PCIe-MI message payload and headers.

- The maximum message body size includes the IC bit, the message integrity check field, the message type field, and any additional message type-specific header fields required by PCIe-MI. Refer to the PCI Express Base Specification for any additional restrictions on message body sizes.

### 9.6 Multiple MCTP physical transports

- In order to facilitate identification of PCle-compatible components that are accessible via multiple physical transports, endpoints that support PCle-MI shall support the Get Endpoint UUID MCTP command.

- Otherwise, this specification does not define any additional behaviors related to communicating with endpoints that support PCIe-MI over MCTP that may be accessed through more than one type of MCTP physical transport on a given MCTP network.

# 10 ANNEX A (informative) Change Log

| Version | Date       | Description     |

|---------|------------|-----------------|

| 1.0.0   | 2025-06-12 | Initial release |